AMD EPYC Venice: до 256 ядер и 512 потоков в серверных CPU на Zen 6

В сеть утекли новые данные о серии серверных процессоров AMD EPYC 9006 Venice, которые станут первыми чипами компании, выпущенными по 2-нм техпроцессу TSMC. На фоне предстоящего запуска в 2025 году, начали появляться подробности о конфигурации, архитектуре и потреблении новинок. Утечки поступили с азиатских форумов, включая Baidu, а также от источников, близких к серверным ОЕМ-партнёрам AMD.

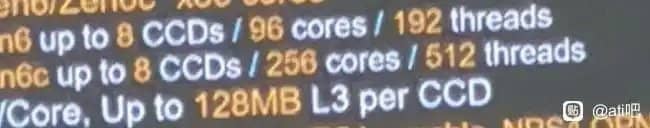

Согласно этим данным, линейка будет разделена на Zen 6 и Zen 6C-модификации, как это было ранее с Zen 4/5 и Zen 4C/5C. Стандартные Zen 6-чипы получат до 96 ядер и 192 потока, в то время как уплотнённые Zen 6C-модели обещают до 256 ядер и 512 потоков — вдвое больше, чем максимум у текущих процессоров Turin. Архитектура предполагает использование до 8 CCD-блоков на чипе, каждый из которых содержит 12 ядер.

Отдельного внимания заслуживает объём кэша третьего уровня: сообщается, что каждый CCD будет содержать до 128 МБ L3, что эквивалентно 2 МБ кэша на ядро в вариантах Zen 6C. Центральный IOD будет расширен для увеличения I/O-возможностей, включая поддержку 12- и 16-канальной DDR5-памяти. Платы с сокетами SP7 и SP8 разделят линейку по уровням: SP7 — для высокопроизводительных HPC-сценариев, SP8 — для более энергоэффективных решений.

Интерес вызывают и TDP-показатели будущих EPYC-чипов: по данным источника Bionic_Squash, Zen 6C на SP7 может достигать 600 Вт, тогда как SP8-версии останутся в пределах 350–400 Вт. Это резкий рост по сравнению с Zen 5-серией, но он оправдан плотностью вычислительных блоков.