AMD открывает эру дизайна многоуровневых микросхем, начиная с Zen 3 с технологией 3D Stacked V-Cache

AMD подробно описала свои будущие технологии многоуровневого проектирования микросхем, которые будут интегрированы в процессоры следующего поколения, такие как грядущие чипы Zen 3 с технологией 3D V-Cache.

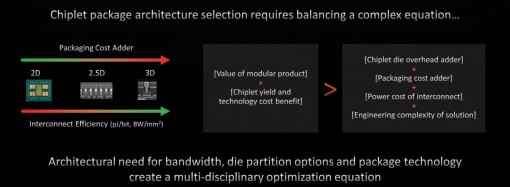

На HotChips 33 компания рассказала о существующих конструкциях чиплетов и о том, что нас ждет в будущем с точки зрения развития многослойных чипов. В настоящее время в разработке находятся 14 архитектур пакетов для чиплетов для различных продуктов, которые уже были выпущены или выйдут в ближайшее время. AMD заявляет, что выбор упаковки и архитектура чиплета зависят от производительности, мощности, площади и стоимости соответствующего продукта.

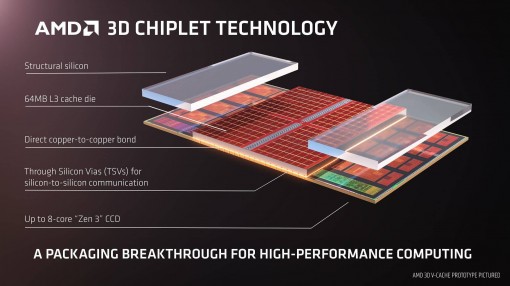

По словам AMD, в 2021 году будет впервые представлена архитектура 3D Chiplet. Первым продуктом, в котором будет реализована эта технология, станет ядро AMD Zen 3, которое будет иметь кэш SRAM поверх основной матрицы Zen 3 CCD. Использование технологии 3D-чиплетов также увеличивает плотность межсоединений, сохраняя при этом наименьшую мощность и площадь.

AMD рассказала, как интегрирует 3D V-Cache поверх своей ПЗС Zen 3. Это достигается за счет использования Micro Bump (3D) и нескольких межсоединений TSV, как упоминалось выше. В межкомпонентном соединении используется совершенно новое гидрофильное соединение диэлектрик-диэлектрик с прямым соединением CU-CU, которое было разработано и совместно оптимизировано в тесном сотрудничестве с TSMC. Два отдельных силикона (чиплета) склеиваются вместе с использованием этой технологии.

Согласно AMD, гибридная связь имеет шаг 9 микрон и внутреннюю часть, аналогичную TSV, которая немного меньше, чем межсоединение Intel Forveros с шагом 10 микрон. Энергоэффективность межсоединений оценивается более чем в 3 раза по сравнению с Micron Bump 3D, плотность межсоединений более чем в 15 раз выше, чем у Micron Bump 3D, и эти 3D-чиплеты также обеспечивают лучший сигнал / мощность благодаря снижению емкости TSV и индуктивности.

AMD также подчеркивает, что DRAM на процессоре — это только начало того, чего они могут достичь с помощью трехмерного стекирования. В будущем AMD рассчитывает использовать 3D-стекирование для стекирования ядер поверх ядер, IP поверх IP, и все станет действительно сумасшедшим, когда макроблоки можно будет наложить 3D поверх других макроблоков.