TSMC раскрыла детали 2nm N2: прирост производительности на 15% и снижение энергопотребления на 30%

![]()

TSMC представила новые подробности о своей передовой технологии 2nm N2, которая обещает гигантский скачок производительности и энергоэффективности. На брифинге в рамках конференции IEEE IEDM в Сан-Франциско компания рассказала о ключевых особенностях технологии, включая нано-листовую архитектуру GAA (Gate-All-Around).

Переход с FinFET на нано-листы позволил TSMC улучшить управление током, благодаря чему технологию можно настраивать под конкретные задачи. Каждый из узких кремниевых слоёв окружён затвором, что обеспечивает более точный контроль и повышенную производительность.

Ключевые достижения 2nm N2:

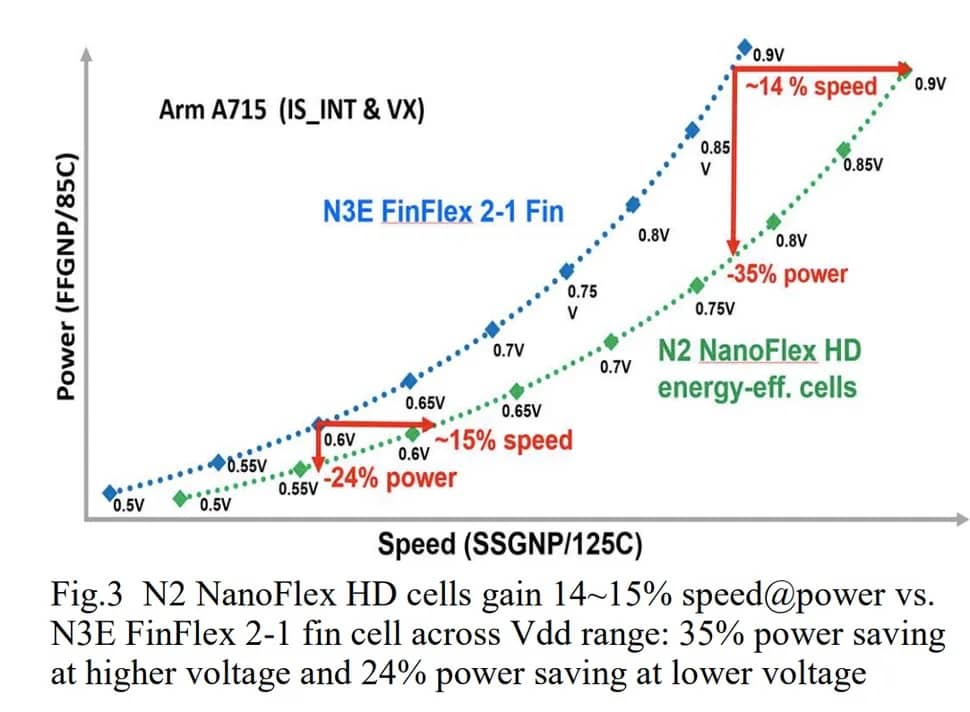

- 15% прирост производительности по сравнению с 3nm.

- Снижение энергопотребления на 30%.

- 1.15-кратное увеличение плотности транзисторов благодаря NanoFlex, оптимизирующему размещение логических элементов.

TSMC прогнозирует массовое производство N2 уже в 2025 году, но с этим связаны и рост цен. Стоимость одного 2nm вафера составит около $25,000–30,000, что на 10% выше, чем у 3nm (около $20,000).

Несмотря на высокую стоимость и изначально ограниченные объёмы производства, технология N2 ожидает широкое внедрение у таких гигантов, как Apple и NVIDIA.

TSMC N2 демонстрирует огромный потенциал для следующего поколения чипов, что позволит индустрии выйти на новый уровень производительности и энергоэффективности.