Synopsys продвигает LPDDR6 с рекордной пропускной способностью на базе техпроцесса TSMC N2P

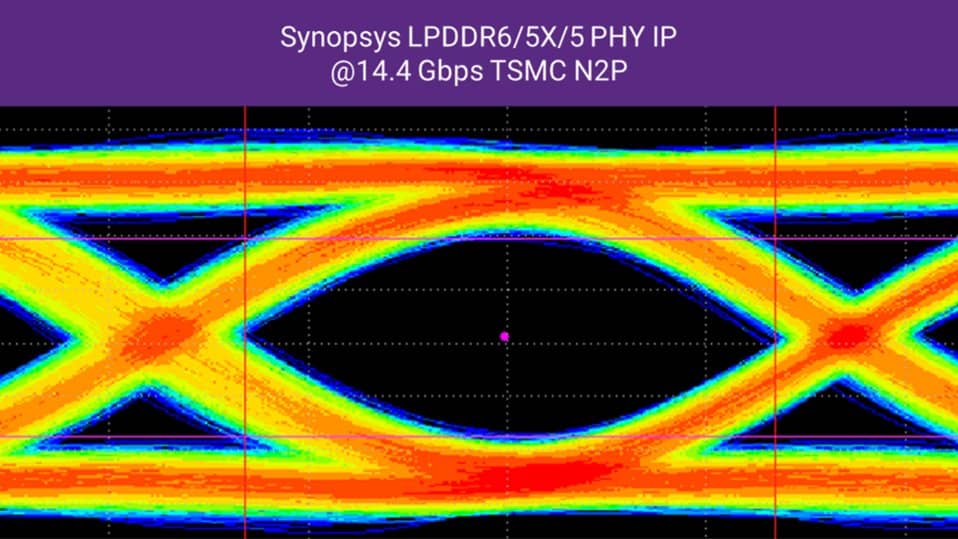

Компания Synopsys сообщила об успешной bring-up-проверке IP-блока LPDDR6, созданного с использованием техпроцесса TSMC N2P. Этот этап означает, что интеграция IP прошла первый запуск на кремнии и готова к дальнейшему лицензированию партнёрами. По заявлению Synopsys, контроллер и PHY-интерфейс нового решения уже показывают пропускную способность до 86 ГБ/с, что соответствует актуальному уровню стандарта JEDEC.

Благодаря особенностям N2P, включающим продвинутые металлические стеки и I/O-библиотеки, удалось добиться снижения энергопотребления и сокращения площади чипа. Это делает новый IP особенно актуальным для встраиваемых AI-платформ и энергоэффективных решений, включая смартфоны и ноутбуки. Устройство включает контроллер с поддержкой всех функций JEDEC, включая управление таймингом и переходами в энергосберегающие состояния.

Отдельно подчёркивается, что процесс N2P обеспечивает лучшие на рынке PPA-показатели (performance, power, area), что позволяет обеспечить высокую плотность размещения логики, требуемую для LPDDR6. Сама спецификация стандарта предусматривает до 14,4 ГБ/с на пин, что потенциально может вывести пропускную способность выше 115 ГБ/с при оптимальной реализации.

Выход LPDDR6 в массовый сегмент ожидается в 2026 году, и Synopsys рассчитывает, что её IP-блок станет ключевым компонентом в мобильных и AI-ориентированных SoC. Новинка демонстрирует, как передовые литографические технологии могут ускорить внедрение новых стандартов памяти в коммерческие устройства.