AMD обновляет технологию D2D-интерконнекта — Strix Halo стал предвестником Zen 6

AMD готовит серьёзный прорыв в архитектуре Zen 6, и первые элементы этого подхода уже появились в APU Strix Halo. Компания решила модернизировать технологию межкристального соединения D2D (die-to-die), отказавшись от устаревшей схемы с SERDES в пользу более энергоэффективного и быстрого решения.

С момента Zen 2 AMD использовала SERDES PHY — сериализаторы/десериализаторы, передающие данные между CCD и I/O-чипами через быстрые последовательные линии. Однако такая система требует дополнительных затрат энергии и увеличивает задержки из-за этапов кодирования, восстановления тактов и преобразования потоков данных. В условиях роста требований, особенно с добавлением NPU и новых типов памяти, AMD потребовалось решение с более низким оверхедом.

В APU Strix Halo применяется новая архитектура с использованием TSMC InFO-oS (Integrated Fan-Out on Substrate) и распределённого слоя проводников RDL (Redistribution Layer). Вместо передачи по последовательным линиям, как в SERDES, данные между кристаллами передаются по параллельным тонким проводникам, размещённым на интерпозере под кристаллами. Это сокращает задержки и снижает энергопотребление, а также позволяет масштабировать пропускную способность за счёт добавления портов.

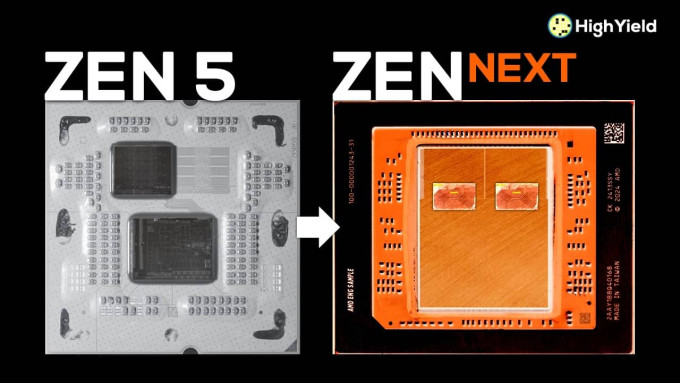

Указание на новую систему можно найти по особым структурным элементам Strix Halo: отсутствию блока SERDES и появлению характерного поля контактных площадок, типичных для Fan-Out-интерпозеров. Именно это может лечь в основу интерконнекта будущих процессоров Zen 6, поскольку подход уже продемонстрировал высокую эффективность.

Несмотря на технические сложности с многослойной маршрутизацией в RDL, новая реализация открывает путь к снижению задержек, более высокой плотности соединений и экономии энергии. Всё указывает на то, что Zen 6 станет первой основной платформой AMD с полностью обновлённой схемой межкристального обмена.